AMD openSIL Zen 6 Ryzen Medusa

AMD has officially confirmed that its upcoming Zen 6 architecture will feature openSIL (Open-Source Silicon Initialization Library) support — a major step toward open-source firmware development in both consumer and enterprise computing.

The confirmation came during the Open Compute Project (OCP) Global Summit 2025, where AMD detailed plans to integrate openSIL into its next-generation EPYC ‘Venice’ and Ryzen ‘Medusa’ processors.

This move represents a significant evolution in AMD’s firmware strategy, transitioning away from proprietary AGESA code and toward a more transparent, modular, and community-driven system.

What Exactly Is openSIL?

In simple terms, openSIL is AMD’s new open-source firmware framework, designed to replace its long-running AGESA (AMD Generic Encapsulated System Architecture).

Unlike AGESA, which is fully closed and vendor-controlled, openSIL is completely open-source, meaning developers and manufacturers will be able to access, audit, and optimize the firmware at a much deeper level.

According to AMD, the openSIL framework is built around three modular components:

- Silicon Layer – Handles CPU-specific initialization (power management, cache, etc.)

- Platform Layer – Deals with system-level components like motherboards and I/O subsystems

- Utilities Layer – Includes helper functions and standard libraries

This modular structure allows for cleaner code, faster development, and improved security through community review.

When will openSIL arrive?

AMD confirmed that openSIL will debut first in the server segment:

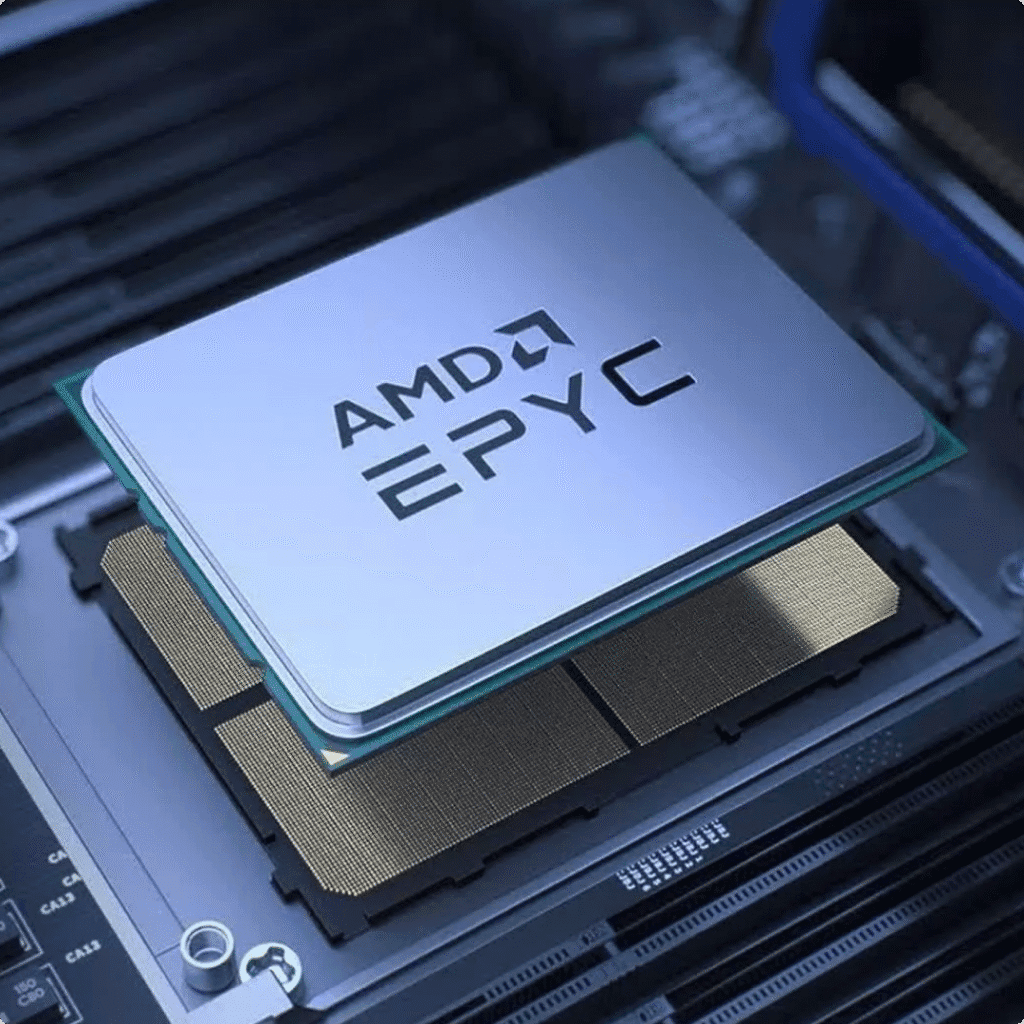

- 🟣 EPYC “Venice” (Zen 6) – Launching in 2026, will be the first AMD CPU line to use openSIL.

- 🔵 Ryzen “Medusa” (Zen 6) – The desktop version, expected in the first half of 2027, will also support openSIL at launch.

This staggered rollout lets AMD test and stabilize openSIL in the enterprise environment before bringing it to consumer hardware.

Why It Matters

AMD’s move to openSIL could reshape how firmware works across the PC ecosystem. Here’s why it’s such a big deal:

1. Transparency and Security

Open-source code can be reviewed by anyone, reducing vulnerabilities and building trust — crucial for data centers and enterprise environments.

2. Customization and Flexibility

Motherboard makers, system integrators, and even advanced users could eventually tune or optimize firmware for performance and stability — something not possible with closed firmware.

3. Faster Updates and Bug Fixes

With a modular codebase, firmware updates could roll out faster and more consistently across platforms, improving long-term stability.

4. Ecosystem Growth

If AMD’s openSIL model succeeds, it may encourage other vendors (like Intel or ARM partners) to consider similar open frameworks.

Zen 6: What We Know So Far

The Zen 6 microarchitecture will succeed Zen 5, powering both Ryzen ‘Medusa’ desktop CPUs and EPYC ‘Venice’ data-center processors.

Here’s what early information suggests:

- Architecture: 4 nm process node

- Core counts: Expected to scale up to 24 cores for consumer CPUs (two 12-core chiplets)

- Cache improvements: Larger L3 cache per CCD (reportedly up to 48 MB)

- Platform: Likely AM5 or a successor socket for Ryzen Medusa

- Server support: SP5 platform continuation for EPYC Venice

While final specs are yet to be confirmed, AMD’s early announcements emphasize efficiency gains, better multi-thread scaling, and improved AI and data-handling capabilities.

Impact on Creators and Professionals

For content creators, video editors, and designers, openSIL could indirectly improve performance and reliability.

- Firmware stability: Fewer random system errors or BIOS conflicts during heavy workloads.

- Faster optimization: Motherboard vendors can fine-tune performance profiles more easily.

- Better compatibility: As firmware becomes more standardized, future upgrades may require less manual tweaking.

For professionals running render farms, virtual servers, or editing suites, this could translate to longer system lifespans and fewer downtime issues.

What Comes Next

AMD has outlined a multi-year roadmap for integrating openSIL across its platforms. The timeline looks roughly like this:

| 2025 | Zen 5 | Ryzen Granite Ridge / EPYC Turin | AGESA |

| 2026 | Zen 6 | EPYC Venice | openSIL (v1.0) |

| 2027 | Zen 6 | Ryzen Medusa | openSIL (v1.1) |

AMD also plans to make openSIL available on GitHub, encouraging developers and OEMs to participate in firmware testing and contributions — further strengthening community collaboration.

Final Thoughts

AMD’s confirmation of openSIL for Zen 6 marks a turning point in the company’s approach to firmware transparency and long-term platform stability.

With EPYC Venice leading the charge in 2026 and Ryzen Medusa following in 2027, AMD is not just refining CPU performance — it’s redefining the firmware ecosystem around it.

For consumers, creators, and system builders, this could mean greater stability, longer platform support, and faster innovation across desktop and server computing.

AMD openSIL Zen 6 Ryzen Medusa *The information provided above is not entirely correct. There is always the possibility of making an error when adding information. In general, we gather information from the manufacturer’s website and other